PRIMEIRO SINAL DE REINICIALIZAÇÃO NO CIRCUITO DO COMPUTADOR

RSMRST#

Quando Power,Bios,Ec estiverem OK, o RSMRST# será Hi. Em outras palavras, este pino vai para baixo somente quando o sistema é reiniciado.

Quando o SIO(EC) receber +V_RTC

, o cristal funcionará.

1. O RTC deve estar oscilando (32,768 KHz).

2. RTCRST# tem que ser alto.

3. O RSMRST# deve estar inativo (alto).

4. PWRBTN# tem um gatilho.

5. LOW_BAT# deve estar inativo (alto).

Se este 5 estiver presente, o EC emitirá SLP_S3# /SLP_S5, no antigo ICH SLP_S3 e SLP_S5 gerará diretamente para o ICH.

Quando Todos+V?S/+V? as potências estão prontas, PWR_GOOD vai ligar para alta para ligar as potências da CPU (+VCCP e +VCC_CORE).

SB/PCH Power good—>SB/PCH pwr_btn—>PCH RUN

SUSB# from PCH toSIO puxa o sinal SLP_S3# O sinal é usado para desligar/ligar através do transistor de porta lógica ou IC

SUSC# do PCH para SIO puxa o sinal SLP_S5# O sinal é usado para desligar/ligar através do transistor de porta lógica ou IC

ICH/SB,MCH & CPU Verificação de Sinal

IMVP_PWRGD => CLK_ENABLE# => RESET_OUT#=> ICH_PWRGD => PLTRST# = > PCI_RST=> H_PWRGOOD

CPU gera o primeiro ciclo para ler o código do BIOS

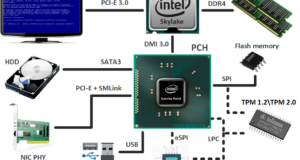

Barramento da CPU DMI LPC SPI

CPU ===> GMCH===> ICH===>SIO ===> BIOS

CPU MASTER POWER

VR_ON Enable —> +VCCORE 08VS a 1,5VS

A memória +VTT e +V1.5VS (DDR3) está ok, o PGOOD VTT_PWRGD puxa o alto para a CPU primeiro do que o ICH liga o H_PWRGD ao alto, então NB liga o CPURST# para redefinir a CPU.

Crystal clock Oscilator CLOCK RESUMO

(1) 32.768KHz para SIO Necessário +V_RTC e para ICH(chipset) também Necessário +V_RTC

(2) 49.152MHz para (controlador de áudio) Necessário +V3S

(3) 27MHz para chip gráfico (controlador de vídeo) Necessário +V3S

(4) 14.318MHz para (Gerador de Relógio) Necessário +V3S

Certifique-se de que o cristal está oscilando para EC(SIO),SB/ICH/PCH e VGA ou não será necessário pós

Gerador de Relógio

Elementar

1) Alimentação: +V3S

(2 ) Cristal: 14.318MHz

(3) Controle: PCISTOP#, CPUSTOP#_ é HI

Quando +VCC_CORE estiver pronto, CLKEN# irá para alto para habilitar o gerador de relógio e ativar todos os relógios.

PCI_STOP# e CPU_STOP# devem bater alto, caso contrário alguns relógios serão desligados.

Clock out –>SIO(EC)–>PCH/SB–>NB–>CPU

LPC_Frame–>Sinal de saída SB está alto

Nota O sinal alto pode ser identificado medindo 3.3V

Potência disponível por experiências de adiedkhaz

NÃO PERCA

- Leitor scanner I2C

- Intel Boot Guard

- Desktops Inspiron Códigos de bipe/LED

- Bios Beep Code Dell inspiron desktops

- Dell códigos de erro de diagnóstico para notebooks e tablets 2015 e 2016

- Solucionar Erro 2502/2503 na Instalação de Programas no Windows

- Manuseio Osciloscópio

- POST Beep sintomas – Think Centre

- Abreviações em diagramas de placas de notebooks ou desktop

- Abreviações mais importantes do esquema de notebook

Zenilto Soluções em Tecnologia

Zenilto Soluções em Tecnologia